Loading...

스티커

구분

특허/실용/디자인/상표

특허등록일자 2017-04-04

취득구분 등록

기술분류 농림/수산

지식재산유형 국내출원

등록번호(특허) 30-0902125

출원(등록)번호 30-2017-0003373

출원형태

발명자수 1

DOI 값

주요내용

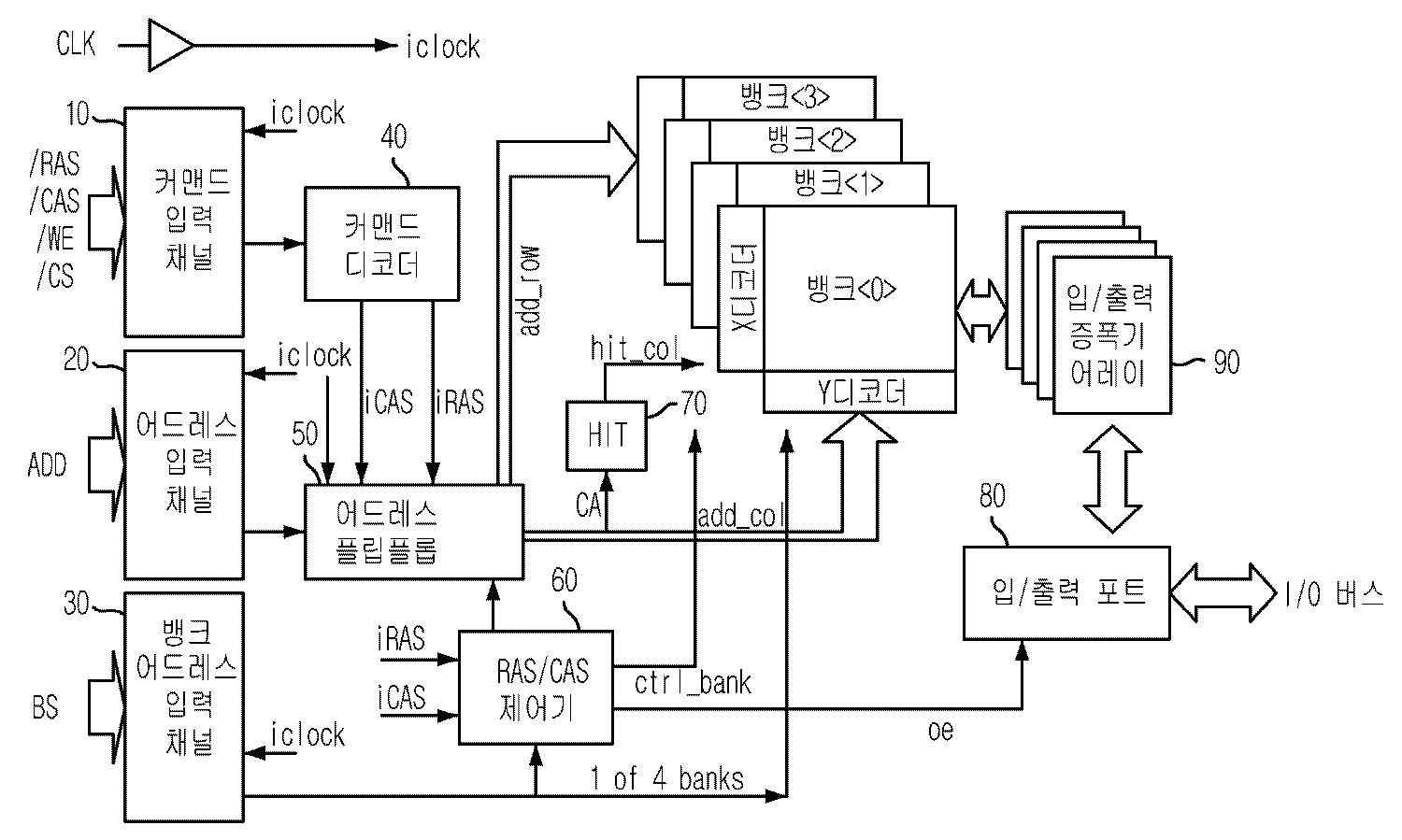

본 발명은 반도체 메모리 설계 기술에 관한 것으로, 특히 DRAM(Dynamic Random Access Memory) 아키텍쳐(Architecture)에 관한 것이다. 본 발명은 메모리 액세스에 수반되는 전력 소모를 줄일 수 있는 DRAM을 제공하는데 그 목적이 있다. 본 발명에서는 로우 어드레스 및 컬럼 어드레스를 모두 입력받아 저장한 다음, 컬럼 어드레스의 MSB(Most Significant Bit) 일부 비트를 디코딩하여 활성화할 페이지 영역을 결정하는 방식을 채용하였다. 즉, 로우 어드레스에 대응하는 한 페이지 전체를 활성화하는 것이 아니라, 실제 액세스가 이루어질 메모리 셀이 포함된 일부 페이지 영역을 선택적으로 활성화한다. 최근 시스템의 메모리 활용 기능 중 부가 레이턴시(additive latency, AL) 규격에 의하면 로우 어드레스 입력 후, 다음 클럭에서 곧바로 컬럼 어드레스 입력이 이루어지고, 이후 로우 어드레스 및 컬럼 어드레스 디코딩이 가능하여 시스템 환경을 크게 바꾸지 않고도 본 발명의 구현이 가능하다. 디램, 저전력, 컬럼 어드레스, MSB 코드, 활성화

발명자 정보

| 이름 | 소속 |

|---|---|

| 이정현 | 전남대학교 원예생명공학과 |